# Timed Weak Simulation Verification and its application to Stepwise Refinement of Real-Time Software

#### Satoshi Yamane

Graduate School of Natural Science Kanazawa University Kanazawa City, Japan, ZIP/CODE 920-1192 Email: syamane@is.t.kanazawa-u.ac.jp

**Abstract.** Real-time software runs over real-time operating systems, and guaranteeing qualities are difficult. In this paper, we propose timed weak simulation relation verification and apply it to a refinement design method of real-time software. Moreover, we apply our proposed method to general real-time software scheduled by fixed-priority preemptive policy.

#### 1 Introduction

As real-time software is reactive and concurrent, and its timing conditions are strict, it is difficult to design real-time software [1]. It is important to specify and verify real-time software. In this paper, we propose timed weak simulation relation verification method based on timed automata [2], and apply it to stepwise refinement of real-time software over fixed priority preemptive schedulers [3]. In general, real-time software is designed by dividing it into tasks [1] In this case, it is difficult to design real-time software by the following points: (1)Real-time software consists of many tasks, which concurrently behave. Moreover, tasks interact with external environments. In this situation, it is useful to distinguish between internal events and external events in the sense of process algebra [4]. (2)In real-time software, stepwise refinement is useful, and it is important to automatically verify whether the concrete specification refines the abstract specification.

From the above results, we propose the followings: (1)We use nondeterministic timed automata, which have internal and external events. We construct real-time software by parallel composition of nondeterministic timed automata. (2)We verify whether the concrete specification refines the abstract specification based on a timed weak simulation.

In general, refinement relations such as language inclusion, timed bisimulation and timed strong simulation are useful as follows: (1)We can easily and naturally verify fairness and regularity as acceptance conditions by language inclusion. But if we specify verification properties using nondeterministic timed automata, language inclusion problems are undecidable [2]. On the other hand, R. Alur proposed an event-clock automata, which is a determinizable of timed automaton [5,6]. But an event-clock automaton is a subclass of a timed automaton, and accepts a finite timed word (though a general timed automaton accepts an infinite timed word). As the determinization of an event-clock automaton causes an exponential blow-up in the number of locations, the verification cost increases. Moreover, we can not verify some deadlock using language inclusion [4,7]. (2)Timed bisimulation relation is useful for verifying a kind of invariant holding between the more concrete specification and the more abstract specification [8]. On the other hand, timed strong simulation relation is useful for verifying stepwise refinement [9]. But when we stepwise develop specifications, we may

add exception procedures to the concrete specification, which are not contained in the abstract specification. Both timed bisimulation relation and timed strong simulation relation are not adequate for this reason.

From the above result, we use timed weak simulation relation in order to verify whether the concrete specification refines the abstract specification.

We survey related works as follows: (1)In 1992, Cerans has shown that timed strong and weak bisimulation equivalence problem for timed automata are decidable [8]. But he has not developed bisimulation algorithms. (2)In 1996, Tasiran and his colleagues have developed the verification algorithm of timed strong simulation relation [9]. But they have not developed a timed weak simulation relation. (3)In 1999, Braberman and his colleagues have developed reachability analysis method of preemptive scheduling using timed automata [10]. But they have not developed refinement verification method.

In this paper, we define a timed weak simulation relation, and propose the verification algorithm of timed weak simulation relation. Moreover we apply our proposed method to general real-time software scheduled by fixed-priority preemptive policy. As it is difficult to treat internal behaviors, timed weak simufation verification methods of timed automata have never been developed before now. Timed weak simulation verification is our original work. The paper is organized as follows: In section 2, we define specification method. In section 3, we define timed weak simulation relation verification method and apply it to stepwise refinement of real-time software. In section 4, we present design supprt system and some example. Finally, in section 5, we present conclusions.

#### Specification of Real-Time Software

In this paper, we specify tasks using nondeterministic timed automata with internal and external events, and construct real-time software by parallel composition of tasks.

#### Syntax and Semantics of Timed Automata

First we define clock as follows:

**Definition 1 (Clock and clock interpretation)** Given a finite set of variables  $X = \{x_1, \ldots, x_n\}$ , a valuation is a function  $v: X \to \mathbb{R}^{+0}$ , which assigns a nonnegative real value to each clock variable. We define  $V^X$  as the set  $[X \to \mathbb{R}^{+0}]$ .  $\mathbf{0}$  denotes the valuation that assigns the value 0 to each  $x \in X$ . For  $\lambda \subseteq X$ ,  $v[\lambda := 0]$  denotes the valuation that assigns the value 0 to each  $x \in \lambda$  and agrees with v for all clocks in  $X \setminus \lambda$ . Moreover, for every  $t \in \mathbb{R}^+$ , v + t denotes the clock valuation for which all clocks  $x \in X$  take the value v(x) + t.

#### Definition 2 (Clock constraints)

For a set X of clock variables, the set  $\Psi^X$  of clock constraints  $\psi$  is inductively defined by  $\psi ::= x \sim c \mid \psi_1 \wedge \psi_2$ , where  $\sim \in \{\leq, =, \geq\}$ ,  $c \in \mathbb{N}$ . We write  $v \models \psi$ if the valuation v satisfies the formula  $\psi$ . For each clock  $x \in X$ ,  $c_x(\Psi^X)$  denotes the maximal clock constant in  $\Psi^X$ .

#### Definition 3 (Syntax of timed automata)

A timed automaton **G** is a tuple  $\langle S, \bar{s}, \Sigma, X, inv, E \rangle$ , where

- (1) S is the finite set of locations.

- (2)  $\bar{s} \in S$  is an initial location.

- (3)  $\Sigma = EXT \cup INT$  is the finite set of events, where EXT is the finite set of external events, INT is the finite set of internal events.

- (4) X is the finite set of real-valued variables, called clocks.

- (5)  $inv: S \to \Psi^X$  is the invariant function that assigns  $\Psi^X$  to each location  $s \in S$ .

- (6) E is the finite set of edges. Each edge e is a tuple  $\langle s, \sigma, \psi, \lambda, s' \rangle = e \in E$ consisting of the source location s, the target location s', clock constraint  $\psi \in \Psi^X$ , the set  $\lambda$  of clocks to be reset,  $\sigma \in \Sigma$  is an event, where  $\lambda = \emptyset$  if  $\sigma \in INT$ .

## Next we formally define semantics of timed automata. **Definition 4 (Semantics of timed automata)**

A state of G is a pair  $\langle s, v \rangle$  containing the location  $s \in S$  and the valuation  $v \models inv(s)$ . The set of all states is denoted  $\Omega$ . The initial state is a pair  $\langle \bar{s}, \mathbf{0} \rangle$ . For each state  $\langle s, v \rangle$ , the transition is defined as follows:

1. Discrete transitions:

A run of timed automaton is an infinite sequence as follows:

$$\langle \overline{s}, \mathbf{0} \rangle \xrightarrow{\ell_1} \langle s_1, v_1 \rangle \xrightarrow{\ell_2} \langle s_2, v_2 \rangle \xrightarrow{\ell_3} \cdots$$

$$, where \langle \overline{s}, \mathbf{0} \rangle \text{ is an initial state, } \langle s_i, v_i \rangle \in \Omega \text{ is a state, } \ell_i \in (\Sigma \cup \mathbb{R}^+) \text{ is a label.}$$

In this paper, we assume that timed automaton is nonZeno. It is easy to verify whether a timed automaton is nonZeno or not using HYTECH [11].

Parallel Composition of Timed Automata

In this paper, we construct real-time software by parallel composition of tasks. We define parallel composition of timed automata as follows:

- (1) If the external event of a task is equal to the external event of environments, the task is synchronized with environments by the same external event.

- (2) As internal events of tasks are unobservable from environments, internal events of tasks and events of environments are disjoint.

#### Definition 5 (Parallel composition)

Let be two timed automata  $\mathbf{G_1} = \langle S_1, \bar{s}_1, \Sigma_1, X_1, inv_1, E_1 \rangle$  and  $\mathbf{G_2} = \langle S_2, \bar{s}_2, \Sigma_2, X_2, inv_2, E_2 \rangle$ . The parallel composition of  $G_1$  and  $G_2$  is the timed automaton  $G = \langle \dot{S}, \bar{s}, \Sigma, X, inv, E \rangle$ , where  $\Sigma_1 = EXT_1 \cup INT_1$ ,  $\Sigma_2 = EXT_2 \cup INT_2$ . Here  $INT_1 \cap \Sigma_2 = \Sigma_1 \cap INT_2 = \Sigma_2 \cap INT_2 = \Sigma_1 \cap INT_2 = \Sigma_2 \cap INT_2 =$

- (1)  $S \subseteq S_1 \times S_2$ .

- (2)  $\bar{s} = (\bar{s}_1, \bar{s}_2).$

- (3)  $\Sigma = EXT \cup INT$ , where  $EXT = EXT_1 \cup EXT_2$ ,  $INT = INT_1 \cup INT_2$ .

- (4)  $X = X^A \cup X^B$ .

- (5)  $inv((s_1, s_2)) = inv_1(s_1) \wedge inv_2(s_2)$ .

- (6)  $\langle s, \sigma, \psi, \lambda, s' \rangle \in E$ , where for  $\langle s_1, \sigma, \psi_1, \lambda_1, s'_1 \rangle \in E_1$  and  $\langle s_2, \sigma, \psi_2, \lambda_2, s'_2 \rangle \in E_1$  $E_2$ , each element is as follows:

- (a) When  $\sigma \in \Sigma_1 \cap \Sigma_2$ ,  $s = (s_1, s_2), \psi = \psi_1 \wedge \psi_2, \lambda = \lambda_1 \cup \lambda_2, s' = (s'_1, s'_2).$

- (b) When  $\sigma \in \Sigma_1$  and  $\sigma \notin \Sigma_2$ ,  $s = (s_1, s_2), \psi = \psi_1, \lambda = \lambda_1, s' = (s'_1, s_2).$ (c) When  $\sigma \in \Sigma_2$  and  $\sigma \notin \Sigma_1$ ,  $s = (s_1, s_2), \psi = \psi_2, \lambda = \lambda_2, s' = (s_1, s'_2).$

${\bf 2.3}$   $\,$  Specification Method We decide parameters such as priorities and timing constraints by V. Braberman's method [10], which is based on WCRT(Worst Case Response Time) [12].

First we define Worst-Case Response Time as follows:

#### Definition 6 (Worst-Case Response Time)

If every task j, j < i, has higher priority than task i, the worst-case response time  $R_i$  of task i is given as recursive equation (i = 1, ..., n). The (k + 1)th worst-case response time  $Ri^{(k+1)}$  for task i is as follows  $(k \ge 0)$ :

$$R_i^{(k+1)} = \sum_{j=1}^{i-1} (\lceil \frac{R_i^{(k)}}{T_j} \rceil \times C_j) + C_i$$

,where period  $T_i$ , execution time  $C_i$ , deadline  $D_i$  of a periodic task i. We can compute  $R_i = \lim_{k \to \infty} R_i^{(k)}$  as  $Ri^{(0)} = C_i$ .

Using  $R_i$ , we can check whether real-time software is schedulable or not as follows:

Real-time software is schedulable if the following condition is satisfied: For  $\forall i, R_i \leq D_i (i=1,...,n)$  holds true.[12]

Next we specify real-time software using timed automata.

In general, it is not possible to exactly specify preemptive scheduling using timed automata. Therefore, R. Alur and T.A. Henzinger have specified preemptive scheduling using hybrid automata [13]. In this paper, we approximately specify timing constraints by  $c_{min} \leq x \leq c_{max}$  using timed automata, where we set  $c_{min}$  using timing constraints of edges, and set  $c_{max}$  using worst-case response time. Therefore, we can realize the automatic verification of timed weak simulation relation. If we specify real-time software of preemptive scheduling using hybrid automata, it is not possible to automatically verify timed weak simulation [14].

### Refinement Design Method

It is important to design real-time software by stepwise refinement as real-time software is a complex system. In this case, it is important to verify whether the concrete specification is satisfied by the abstract one or not. First we define a timed weak simulation. Next we define the verification method of a timed weak simulation. Finally we explain the stepwise refinement design method of real-time software.

#### A timed weak simulation

First we define observable transitions as follows:

#### Definition 7 (Observable transitions)

For each state  $\langle s, v \rangle \in \Omega$  of timed automaton  $\mathbf{G} = \langle S, \bar{s}, \Sigma, X, inv, E \rangle$ , observable transitions are defined as follows:

Here Let  $\stackrel{\epsilon}{\Longrightarrow}$  if and only if  $(\stackrel{\tau}{\to})^*$ , where  $\Sigma = EXT \cup INT$ ,  $\tau \in INT$ .

(1) For an external event  $\sigma \in EXT$ ,

Define

$$\langle s, v \rangle \stackrel{\sigma}{\Longrightarrow} \langle s', v' \rangle$$

as  $\langle s, v \rangle \stackrel{\epsilon}{\Longrightarrow} \stackrel{\sigma}{\Longrightarrow} \stackrel{\epsilon}{\Longrightarrow} \langle s', v' \rangle$ .

(2) For delay  $\delta_1, \dots \delta_k, \delta \in \mathbb{R}^+$ ,

Define  $\langle s, v \rangle \stackrel{\delta}{\Longrightarrow} \langle s', v' \rangle$  as  $\langle s, v \rangle \stackrel{\epsilon}{\Longrightarrow} \stackrel{\delta_1}{\longleftrightarrow} \cdots \stackrel{\epsilon}{\Longrightarrow} \stackrel{\delta_k}{\Longrightarrow} \stackrel{\epsilon}{\longleftrightarrow} \langle s', v' \rangle$   $(k \ge 0)$ . In this case, a state  $\langle s, v \rangle$  is called stable from environments, and we denote  $\mathbf{wait}(\langle s, v \rangle), \text{ where } \delta = \delta_1 + \cdots + \delta_k$

#### Definition 8 (Timed weak simulation)

Let  $\mathbf{G_1} = \langle S_1, \bar{s}_1, \Sigma_1, X_1, inv_1, E_1 \rangle$  and  $\mathbf{G_2} = \langle S_2, \bar{s}_2, \Sigma_2, X_2, inv_2, E_2 \rangle$  be two timed automata. A timed weak simulation relation from  $\mathbf{G_1}$  to  $\mathbf{G_2}$  is a binary relation  $Sim \subseteq \Omega_1 \times \Omega_2$  if the following three conditions are satisfied. Moreover we denote  $\mathbf{G_1} \preceq \mathbf{G_2}$  if there exists a timed weak simulation relation, where  $\Omega_1$  is the set of  $\langle s_1, v_1 \rangle$ ,  $\Omega_2$  is the set of  $\langle s_2, v_2 \rangle$ ,  $\Sigma_1 = EXT_1 \cup INT_1$ ,  $\Sigma_2 = EXT_2 \cup INT_2$ ,  $s_1, s_1' \in S_1$ ,  $v_1, v_1' \in V^{X_1}$ ,  $s_2, s_2' \in S_2$ ,  $v_2, v_2' \in V^{X_2}$ .

- (1) External event condition:

- $EXT_1 \subseteq EXT_2$ .

- (2) Simulation condition:

For every  $(\langle s_1, v_1 \rangle, \langle s_2, v_2 \rangle) \in Sim$  and for every  $\theta \in (EXT_1 \cup \mathbb{R}^+)$ , if  $\langle s_1, v_1 \rangle \stackrel{\theta}{\Longrightarrow} \langle s_1', v_1' \rangle$  then there exists  $\langle s_2', v_2' \rangle$  such that  $\langle s_2, v_2 \rangle \stackrel{\theta}{\Longrightarrow} \langle s_2', v_2' \rangle$  and  $(\langle s_1', v_1' \rangle, \langle s_2', v_2' \rangle) \in Sim$ .

(3) Initial condition:

$(\langle \bar{s}_1, \mathbf{0} \rangle, \langle \bar{s}_2, \mathbf{0} \rangle) \in Sim.$

#### 3.2 Verification method of a timed weak simulation

We achieve a timed weak simulation by converting this check to a finite check on the finitely many equivalence classes, which is called a region weak simulation relation. First we define a region graph, and next define a region weak simulation, and the conversion technique. Finally we show the verification algorithm of a timed weak simulation.

Region graph Since the number of states is infinite, we cannot possibly build a finite automaton. But if two states with the same location agree on the integral parts of all clock values, and also the ordering of the fractional parts of all clock values, then the runs starting from the two states are very similar. From the above facts, we can construct region graphs, which are finite quotient structures by equivalence relations [2].

First we define equivalence relations of clock values.

#### Definition 9 (Equivalence relations of clock values)

Let  $V^X$  be the set of clock values, and  $\Psi^X$  be the set of clock constraints. For any  $t \in \mathbb{R}^{+0}$ ,  $\lfloor t \rfloor$  denotes the integral part of t, and fract(t) denotes the fractional part of t. For  $v, v' \in V^X$ , v and v' are equivalent iff the following three conditions are satisfied. We denote  $v \cong v'$ .

- (1) For clock  $x \in X$ ,  $\lfloor v(x) \rfloor$  and  $\lfloor v'(x) \rfloor$  are the same, or both v(x) and v'(x) are greater than  $c_x(\Psi^X)$ .

- (2) For all  $x, y \in X$  with  $v(x) \leq c_x(\Psi^X)$  and  $v(y) \leq c_y(\Psi^X)$ ,  $fract(v(x)) \leq fract(v(y))$  iff  $fract(v'(x)) \leq fract(v'(y))$ .

- (3) For  $x \in X$  with  $v(x) \le c_x(\Psi^X)$ , fract(v(x)) = 0 iff fract(v'(x)) = 0.

We use [v] to denote the clock region to which v belongs. Next we define the successor of equivalence classes.

#### Definition 10 (Successor of equivalence classes)

Let  $\alpha$  and  $\beta$  be distinct clock equivalence classes of  $V^X$  and  $\Psi^X$ . For each  $v \in \alpha$  and any  $\delta \in \mathbb{R}^+$ , we define the successor of equivalence classes:

- (1) We denote  $\beta = \mathbf{succ_0}(\alpha)$  iff there exists  $\delta$  such that  $\alpha = \beta$  and  $\delta \in \beta$ .

- (2) We denote  $\beta = \mathbf{succ_1}(\alpha)$  iff there exists  $\delta' \leq \delta$  such that  $\alpha \neq \beta$  and  $v + \delta' \in \alpha \cup \beta$  and  $v + \delta \in \beta$ .

Region is denoted by  $\langle s, [v] \rangle$ , or,  $\langle s, \alpha \rangle$ .

Next we define region graph of timed automaton as follows:

#### Definition 11 (Region graph)

For a timed automaton  $\mathbf{G} = \langle S, \bar{s}, \Sigma, X, inv, E \rangle$ , the corresponding region graph  $\mathbf{R}(\mathbf{G}) = \langle Q, \bar{q}, L, N \rangle$  consists of four tuples:

- (1) the finite set of states Q.

- (2) the initial state  $\bar{q} \in Q$ , where  $\bar{q} = \langle \bar{s}, [\mathbf{0}] \rangle$ .

- (3) the finite set of labels  $L = \Sigma \cup SUCC$ , where SUCC is the set of labels, which represent successor relations of equivalence classes.

- (4) a set of transition relations  $N \subseteq Q \times L \times Q$ . For any  $\langle s, \alpha \rangle$ , a set of transition relations are defined as follows:

- (a) If there exists  $\langle s, v \rangle \xrightarrow{\sigma} \langle s', v' \rangle$  such that  $v' \in \beta$  for each  $v \in \alpha$ , it is possible to transit to  $\langle s', \beta \rangle$  by an event, and we denote  $\langle s, \alpha \rangle \xrightarrow{\sigma} \langle s', \beta \rangle$ .

- (b) If there exists  $\langle s, v \rangle \xrightarrow{\delta} \langle s, v' \rangle$  such that  $\beta = \mathbf{succ_i}(\alpha)$  and  $v' \in \beta$  for each  $v \in \alpha$ , it is possible to transit to  $\langle s, \beta \rangle$  by a time delay, and we denote  $\langle s, \alpha \rangle \xrightarrow{\operatorname{succ_i}} \langle s, \beta \rangle$  (i = 0, 1), where  $\operatorname{succ_i} \in SUCC$ .

Region weak simulation relation We will show that the problem of checking the existence of a timed weak simulation relation is decidable. We achieve this by converting this check to a finite check on the finitely many equivalence classes of an equivalence relation (what we call region weak simulation relation) defined on parallel composition of timed automata. We define a region weak simulation relation on parallel composition of timed automata from the following reasons:

- (1) We can construct all the pairs of  $(\langle s_1, v_1 \rangle, \langle s_2, v_2 \rangle) \in Sim$  as  $\langle (s_1, s_2), v_{12} \rangle$  of parallel compostion of timed automata, where  $s_1$  and  $v_1$  are the node and clock value of timed automaton 1,  $s_2$  and  $v_2$  are the node and clock value of timed automaton 2,  $v_{12}$  is the clock values of parallel composition of timed automaton 1 and 2. Therefore a set of state pairs Sim, which represent region weak simulation relation, is a subset of a set of states of product automaton (parallel composition of timed automata)  $\Omega_{\mathbf{G_1}\parallel\mathbf{G_2}}$ . Namely,  $Sim \subseteq \Omega_{\mathbf{G_1}\parallel\mathbf{G_2}}$ .

- (2) As it is easy to trace the relation between  $v_1$  and  $v_2$ , we trace it by  $v_{12}$  of product automaton.

- (3) If one timed automaton has  $\langle s_1, v_1 \rangle \xrightarrow{\delta} \langle s_1, v_1' \rangle$  and another timed automaton has  $\langle s_2, v_2 \rangle \xrightarrow{\delta} \langle s_2, v_2' \rangle$ , product automaton has  $\langle (s_1, s_2), v_{12} \rangle \xrightarrow{\delta} \langle (s_1, s_2), v_{12}' \rangle$ . Therefore we easily represent two timed automata by product timed automaton.

#### Definition 12 $(R(G_1 \parallel G_2))$

We construct product timed automaton  $G_1 \parallel G_2$  from  $G_1$  and  $G_2$  by parallel composition, where  $EXT_1 \subseteq EXT_2$ . We define the region of region graph  $\mathbf{R}(G_1 \parallel G_2)$  as  $\langle (s_1, s_2), \alpha \rangle$ , where  $s_1 \in S_1$ ,  $s_2 \in S_2$ ,  $\alpha$  is the equivalence class of  $V^{X_1 \cup X_2}$  and  $\Psi^{X_1 \cup X_2}$ . Let  $Q_{G_1 \parallel G_2}$  be the set of equivalence classes on

$\mathbf{G_1} \parallel \mathbf{G_2}$ , where  $\langle (s_1, s_2), \alpha \rangle \in Q_{\mathbf{G_1} \parallel \mathbf{G_2}}$ . With  $\mathbf{R}(\langle s_1, v_1 \rangle, \langle s_2, v_2 \rangle)$ , denote the equivalence class  $\langle (s_1, s_2), \alpha \rangle$  that the state  $(\langle s_1, v_1 \rangle, \langle s_2, v_2 \rangle) \in \Omega_{\mathbf{G_1} \parallel \mathbf{G_2}}$  belongs

For any region  $\langle (s_1, s_2), \alpha \rangle$ , observable transitions are as follows:

(1) For an external event  $\sigma \in EXT$ ,

Define

$$\langle (s_1, s_2), \alpha \rangle \stackrel{\sigma}{\Longrightarrow} \langle (s'_1, s'_2), \beta \rangle$$

as  $\langle (s_1, s_2), \alpha \rangle \stackrel{\epsilon}{\Longrightarrow} \stackrel{\sigma}{\Longrightarrow} \stackrel{\epsilon}{\longleftrightarrow} \langle (s'_1, s'_2), \beta \rangle$ .

(2) For  $succ_i \in SUCC$ ,

Define

$$\langle (s_1, s_2), \alpha \rangle \stackrel{succ_i}{\Longrightarrow} \langle (s'_1, s'_2), \beta \rangle \ (i = 0, 1) \ as \ \langle (s_1, s_2), \alpha \rangle \stackrel{\epsilon}{\Longrightarrow} \stackrel{succ_i}{\Longrightarrow} \stackrel{\epsilon}{\Longrightarrow} \langle (s'_1, s'_2), \beta \rangle.$$

Next we define a region weak simulation relation on region graph  $\mathbf{R}(\mathbf{G}_1 \parallel$  $G_2$ ).

#### Definition 13 (Region weak simulation relation)

We say that  $\chi \subseteq Q_{\mathbf{G_1} \parallel \mathbf{G_2}}$  is a region weak simulation from  $\mathbf{G_1}$  to  $\mathbf{G_2}$  iff for each  $\mathbf{R}(\langle s_1, v_1 \rangle, \langle s_2, v_2 \rangle) \in \chi$ , the following three conditions are satisfied.

(1) For every

$$\sigma \in EXT$$

, if  $\langle s_1, v_1 \rangle \stackrel{\sigma}{\Longrightarrow} \langle s'_1, v'_1 \rangle$ ,  $\langle s_2, v_2 \rangle \stackrel{\sigma}{\Longrightarrow} \langle s'_2, v'_2 \rangle$  and  $\mathbf{R}(\langle s_1, v_1 \rangle, \langle s_2, v_2 \rangle) \stackrel{\sigma}{\Longrightarrow} \mathbf{R}(\langle s'_1, v'_1 \rangle, \langle s'_2, v'_2 \rangle)$  such that  $\mathbf{R}(\langle s'_1, v'_1 \rangle, \langle s'_2, v'_2 \rangle) \in \chi$ .

(2) If wait(

$$\langle s_1, v_1 \rangle$$

), for any  $succ_i \in SUCC$ ,  $\mathbf{R}(\langle s_1, v_1 \rangle, \langle s_2, v_2 \rangle) \stackrel{succ_i}{\Longrightarrow} \mathbf{R}(\langle s_1', v_1' \rangle, \langle s_2', v_2' \rangle)$  such that  $\mathbf{R}(\langle s_1', v_1' \rangle, \langle s_2', v_2' \rangle) \in \chi$   $(i = 0, 1)$ .

(3)  $\mathbf{R}(\langle \bar{s}_1, \mathbf{0} \rangle, \langle \bar{s}_2, \mathbf{0} \rangle) \in \chi$ .

#### Theorem 1 (Timed weak simulation and region weak simulation)

For  $\mathbf{R}(\langle s_1, v_1 \rangle, \langle s_2, v_2 \rangle) \in \chi$ , let  $\mathbf{R}_{\chi} = \{(\langle s_1, v_1 \rangle, \langle s_2, v_2 \rangle) | \mathbf{R}(\langle s_1, v_1 \rangle, \langle s_2, v_2 \rangle) \in \chi$  $\chi$ .  $\mathbf{R}_{\chi}$  is a weak timed simulation relation from  $\mathbf{G_1}$  to  $\mathbf{G_2}$  iff  $\chi$  is a region weak simulation relation from  $G_1$  to  $G_2$ .

**Proof 1** We prove it by dividing it into two cases.

- (I) To prove that if  $\mathbf{R}_{\chi}$  is a weak timed simulation relation from  $\mathbf{G_1}$  to  $\mathbf{G_2}$ ,  $\chi$ is a region weak simulation relation from  $G_1$  to  $G_2$ : Assuming that  $\mathbf{R}_{\chi}$  is a weak timed simulation relation from  $\mathbf{G_1}$  to  $\mathbf{G_2}$ . From the definition, we can directly prove  $\chi$  is a region weak simulation relation from  $\mathbf{\ddot{G}_1}$  to  $\mathbf{\ddot{G}_2}$ .

- (II) To prove that if  $\chi$  is a region weak simulation relation from  $G_1$  to  $G_2$ ,  $R_{\chi}$ is a weak timed simulation relation from  $G_1$  to  $G_2$ : Assuming that  $\chi$  is a region weak simulation relation from  $G_1$  to  $G_2$ . For some  $\theta \in (EXT \cup \mathbb{R}^+)$ ,  $(\langle s_1, v_1 \rangle, \langle s_2, v_2 \rangle) \in \mathbf{R}_{\chi}$  and

$$\langle s_1, v_1 \rangle \xrightarrow{\theta} \langle s'_1, v'_1 \rangle.$$

$\langle s_1, v_1 \rangle \stackrel{\theta}{\Longrightarrow} \langle s'_1, v'_1 \rangle$ . We need to show that there exists  $\langle s'_2, v'_2 \rangle$  such that

$$\langle s_2, v_2 \rangle \stackrel{\theta}{\Longrightarrow} \langle s_2', v_2' \rangle \ and \ (\langle s_1', v_1' \rangle, \langle s_2', v_2' \rangle) \in \mathbf{R}_{\chi}.$$

(1) When  $\theta$  is  $\sigma \in EXT$ :

From the definition of

$$\mathbf{R}(\mathbf{G_1} \parallel \mathbf{G_2})$$

, there exists  $\langle s_2', v_2' \rangle$  such that  $\langle s_2, v_2 \rangle \stackrel{\sigma}{\Longrightarrow} \langle s_2', v_2' \rangle$  and  $(\langle s_1', v_1' \rangle, \langle s_2', v_2' \rangle) \in \mathbf{R}_{\chi}$ .

(2) When  $\theta$  is  $\delta \in \mathbb{R}^+$ :

Let be  $\mathbf{R}(\langle s_1, v_1 \rangle, \langle s_2, v_2 \rangle) = \langle (s_1, s_2), [v] \rangle$  and  $\mathbf{R}(\langle s_1', v_1' \rangle, \langle s_2', v_2' \rangle) = \langle (s_1', s_2'), [v'] \rangle$ . First we define equivalence classes  $\alpha_0, \ldots, \alpha_{k+1}$  corresponding to v as follows:

$$\begin{cases} \alpha_0 = [v] \\ \alpha_{i+1} = \mathbf{succ_1}(\alpha_i) \ (0 \le i \le k) \end{cases}$$

Next we define real values  $\delta_1, \ldots, \delta_k, \delta'$  and clock values  $v^{(0)}, \ldots, v^{(k)}$ corresponding to  $\alpha_i$  as follows:

$$\begin{cases} v^{(0)} = v \\ v^{(i+1)} = v^{(i)} + \delta_{i+1} \in \alpha_{i+1} \ (0 \le i < k) \\ v' = v^{(i)} + \delta' \in \alpha_i \cup \alpha_{i+1} \ (i = k) \end{cases}$$

As there exists k such that  $\delta = \delta_1 + \dots + \delta_k + \delta'$ , there are two cases $(k \ge 0)$ .

(a) k = 0:

In this case, as  $v' \in \alpha_0 \cup \alpha_1$  by  $\delta = \delta'$ , the transition is as follows:

$\langle s_1, s_2, \alpha_0 \rangle \stackrel{succ_i}{\Longrightarrow} \langle s'_1, s'_2, \alpha_i \rangle$ Therefore clearly, there exists  $\langle s'_2, v'_2 \rangle$  such that

$$\langle s_2, v_2 \rangle \stackrel{\delta}{\Longrightarrow} \langle s_2', v_2' \rangle$$

and  $(\langle s_1', v_1' \rangle, \langle s_2', v_2' \rangle) \in \mathbf{R}_{\chi}$   $(i = 0, 1)$ .

We consider the following regions as  $\langle s_1^{(i)}, s_2^{(i)}, v_i \rangle \stackrel{\delta_{i+1}}{\Longrightarrow} \langle s_1^{(i+1)}, s_2^{(i+1)}, v_{i+1} \rangle$ of  $G_1 \parallel G_2 \ (0 \le i \le k)$ .

(i)

$$\langle s_1^{(0)}, s_2^{(0)}, \alpha_0 \rangle = \langle s_1, s_2, [v] \rangle$$

$$(i) \langle s_1^{(0)}, s_2^{(0)}, \alpha_0 \rangle = \langle s_1, s_2, [v] \rangle.$$

$$(ii) \langle s_1^{(i)}, s_2^{(i)}, \alpha_i \rangle \stackrel{succ_1}{\Longrightarrow} \langle s_1^{(i+1)}, s_2^{(i+1)}, \alpha_{i+1} \rangle.$$

(iii)

$$\langle s_1^{(i)}, s_2^{(i)}, \alpha_i \rangle \in \chi$$

.

$\langle s_1^{(k)}, s_2^{(k)}, \alpha_k \rangle \in \chi$  is inductively derived from  $\langle s_1, s_2, [v] \rangle$ . As  $v' \in \alpha_k \cup \alpha_{k+1}$  by  $\delta = \delta_1 + \dots + \delta_k + \delta'$ , we get the following transition:  $\langle s_1^{(k)}, s_2^{(k)}, \alpha_k \rangle \stackrel{succ_j}{\Longrightarrow} \langle s_1', s_2', \alpha_{k+j} \rangle$ . Therefore clearly there exists  $\langle s_2', v_2' \rangle$  such that

$$\langle s_2, v_2 \rangle \stackrel{\delta}{\Longrightarrow} \langle s_2', v_2' \rangle$$

and  $(\langle s_1', v_1' \rangle, \langle s_2', v_2' \rangle) \in \mathbf{R}_{\chi}$   $(j = 0, 1)$ .

Verification algorithm of a timed weak simulation. We define the verification algorithm of a timed weak simulation as follows:

#### Definition 14 (Verification algorithm of a timed weak simulation)

For the concrete specification  $G_{I}$ , and the abstract specification  $G_{H}$ , we construct  $G_L \parallel G_H$ , and the region graph  $R(G_L \parallel G_H)$ . In this case, we define the verification algorithm in order to verify whether there exists a timed weak simulation from  $G_L$  to  $G_H$ . Basically first we define  $\chi^{(0)}$ , and inductively compute  $\chi^{(k+1)}$  from  $\chi^{(k)}$ . First if  $EXT_1 \nsubseteq EXT_2$ , there does not exists a timed weak simulation relation. If  $EXT_1 \subseteq EXT_2$ , we compute the followings:

(1) First we compute the relation  $\chi^{(0)} = Q_{\mathbf{G_L} \parallel \mathbf{G_H}}$ , and initialize k by k := 0.

- (2) Next we inductively compute  $\chi^{(k+1)}$  from  $\chi^{(k)}$  by repeating the following procedures  $(k \ge 0)$ .

- (a)  $\chi^{(k+1)} = \emptyset$ .

- (b) If  $\mathbf{R}(\langle s_1, v_1 \rangle, \langle s_2, v_2 \rangle) \in \chi^{(k)}$ , we set  $\chi^{(k+1)} = \chi^{(k+1)} \cup \{\mathbf{R}(\langle s_1, v_1 \rangle, \langle s_2, v_2 \rangle)\}$  when the two following conditions are satisfied.

- (i) For every  $\sigma \in EXT$ , if there exists  $\langle s'_1, v'_1 \rangle$  such that  $\langle s_1, v_1 \rangle \stackrel{\sigma}{\Longrightarrow} \langle s'_1, v'_1 \rangle$ ,  $\langle s_2, v_2 \rangle \stackrel{\sigma}{\Longrightarrow} \langle s'_2, v'_2 \rangle$ ,  $\mathbf{R}(\langle s_1, v_1 \rangle, \langle s_2, v_2 \rangle) \stackrel{\sigma}{\Longrightarrow} \mathbf{R}(\langle s'_1, v'_1 \rangle, \langle s'_2, v'_2 \rangle)$ , and  $\mathbf{R}(\langle s'_1, v'_1 \rangle, \langle s'_2, v'_2 \rangle) \in \chi^{(k)}$ .

- (ii) If  $\mathbf{wait}(\langle s_1, v_1 \rangle)$ , for every  $succ_i \in SUCC$ ,  $\mathbf{R}(\langle s_1, v_1 \rangle, \langle s_2, v_2 \rangle) \stackrel{succ_i}{\Longrightarrow} \mathbf{R}(\langle s_1', v_1' \rangle, \langle s_2', v_2' \rangle)$  and  $\mathbf{R}(\langle s_1', v_1' \rangle, \langle s_2', v_2' \rangle) \in \chi^{(k)}$  (i = 0, 1).

- $and \mathbf{R}(\langle s'_1, v'_1 \rangle, \langle s'_2, v'_2 \rangle) \in \chi^{(k)} \ (i = 0, 1).$ (c) If  $\chi^{(k+1)} = \chi^{(k)}$ , go to (3). If  $\chi^{(k+1)} \neq \chi^{(k)}$ , set k := k + 1, and return (2)(a).

- (3) If  $\chi^{(k+1)}$  includes  $\mathbf{R}(\langle \bar{s}_1, \mathbf{0} \rangle, \langle \bar{s}_2, \mathbf{0} \rangle)$ , we decide  $\chi$  is a timed weak simulation relation. If not so, we decide  $\chi$  is not a timed weak simulation relation.

As this algorithm can be formalized as the greatest fixpoint computation, the algorithm terminates.

#### 3.3 Stepwise refinement design method

We represent both the abstract specification and the concrete one by nondeterministic timed automata, and verify the consistencies between them by a timed weak simulation relation.

#### Definition 15 (Stepwise refinement design method)

The stepwise refinement design method of real-time software consists of the following procedures.

- (1) First we decide task priorities and parameters by WCRT, and specify  $\mathbf{TASK_i^{(0)}}$  by timed automata  $(i=1,\ldots,n)$ , where n is a number of tasks and (0) is the level of refinement.

- (2) Next we refine  $\mathbf{TASK_i^{(k)}}$  into  $\mathbf{TASK_i^{(k+1)}}$ , and specify  $\mathbf{TASK_i^{(k+1)}}$  by timed automata  $(k \ge 0)$ .

- (3) Finally, we construct  $\mathbf{SOFT^{(k)}} = \mathbf{TASK_1^{(k)}} \parallel \cdots \parallel \mathbf{TASK_n^{(k)}}$  and  $\mathbf{SOFT^{(k+1)}} = \mathbf{TASK_1^{(k+1)}} \parallel \cdots \parallel \mathbf{TASK_n^{(k+1)}}$ . We revise  $\mathbf{SOFT^{(k+1)}}$  until there exists a timed weak simulation relation from  $\mathbf{SOFT^{(k+1)}}$  to  $\mathbf{SOFT^{(k)}}$ .

- (4) We repeat the above step (1)-(3), and specify the final one.

#### 4 Example of refinement design

We show our proposed method effective by a plant system. We have implemented our proposed method as design support system. The design support system is implemented by C++ language(7000 lines) on Sun Blade1000(CPU UltraSPARC-III 900MHz, Main memory 1GB). The plant system is an embedded real-time system, and behaves by fixed priority preemptive scheduling. The plant system samples data from Sensor, and controls Valve, and outputs information on Display. If Sensor is in bad condition, this information is announced

to administrator by Lamp. Even if Sensor is in bad condition, the plant system continue to behave by control data. The real-time software of the plant system consists of two periodic tasks such as SAMPLER and MANAGER. The two tasks communicate with each other by QUEUE. In this paper, we think the plant system is implemented by rate monotonic scheduling. Therefore this rate monotonic scheduling algorithm assigns priorities to tasks based on their periods: the shorter the period, the higher the priority. Moreover, we assume  $D_i = T_i$ (i = 1, 2). We compute WCRT(Worst Case Response Time) [12]. From the results, we can determine two tasks are schedulable. The parameters are shown as follows: SAMPLER has parameters such as  $T_i = 20$ ,  $C_i = 6$ ,  $B_i = 1$ ,  $R_i = 7$ . MANAGER has parameters such as  $T_i = 30$ ,  $C_i = 10$ ,  $B_i = 0$ ,  $R_i = 16$ .

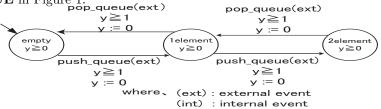

**4.1 Specification of the plant system**We design the plant system, and specify it by timed automata. External events are classified into three types such as system  $call(start_i, end_i, push\_queue,$  $pop\_queue$ ), task control( $dispatch_i$ ) and API(APplication Interface)( $read\_sensor$ , write\_lamp, write\_display, write\_valve). Next we show the shared resource QUEUE in Figure 1.

Fig. 1. Specification of the shared resource  $\mathbf{QUEUE}$

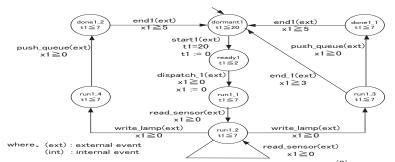

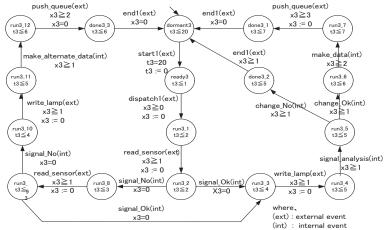

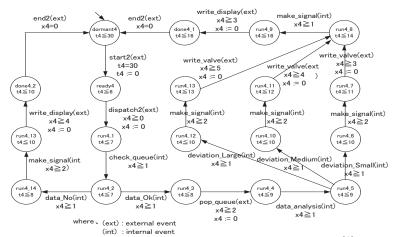

Next we design the abstract specifications  $SAMPLER^{(0)}$  and  $MANAGER^{(0)}$ , and specify them by timed automata, and show them in Figure 2 and 3. In abstract specification, we specify only external events and abstract behaviors. For example, we specify  $SAMPLER^{(0)}$  by nondeterministically behaving  $write\_lamp$ . Finally we design the concrete specifications  $SAMPLER^{(1)}$  and  $MANAGER^{(1)}$ . and show them in Figure 4 and 5. We refine the abstract specification into the concrete one by adding internal behaviors, transforming nondeterministic behaviors into deterministic behaviors and specifying detailed timing constraints. For example,  $SAMPLER^{(1)}$  executes read\_sensor once or twice, and if it fails, **SAMPLER**<sup>(1)</sup> executes  $make\_alternate\_data$ . As the deviation of control data is larger the processing of write\_valve takes longer time, in MANAGER<sup>(1)</sup>, deviation\_Small takes 1, deviation\_Medium takes 2 and deviation\_Large takes

Fig. 2. Specification of the periodic task  $SAMPLER^{(0)}$

Fig. 3. Specification of the periodic task  $MANAGER^{(0)}$

Fig. 4. Specification of the periodic task SAMPLER<sup>(1)</sup>

Fig. 5. Specification of the periodic task  $\mathbf{MANAGER}^{(1)}$

**4.2** Verification experiment We verify whether  $SOFT^{(1)} \leq SOFT^{(0)}$  holds true or not using our design support system, where the abstract specification is defined as  $SOFT^{(0)} = SAMPLER^{(0)}$  $MANAGER^{(0)} \parallel QUEUE$ , the concrete specification is defined as  $SOFT^{(1)} =$ SAMPLER<sup>(1)</sup> | MANAGER<sup>(1)</sup> || QUEUE. We measured required memory=325744kB and execution time=62.30min using ps command. In region graph  $\mathbf{R}(\mathbf{SOFT^{(1)}} \parallel \mathbf{SOFT^{(0)}})$ , the number of the equivalence classes is 62367, the number of regions of  $Q_{\mathbf{SOFT}^{(1)}||\mathbf{SOFT}^{(0)}|}$  is 1645498 and the number of members of region weak simulation  $\chi$  is 1408290. The members of the set  $\chi$ , which are contained in the region weak simulation relation. As an initial region is contained in  $\chi$ ,  $SOFT^{(1)} \leq SOFT^{(0)}$  is satisfied. Namely, there exists a timed weak simulation from the concrete specification to the abstract one. Though the verification cost is large, we can specify both the abstract and the concrete specifications of real-time software using timed automata, and automatically verify whether there exists a timed weak simulation from the concrete specification to the abstract one.

5 Conclusion In this paper, we have proposed the following stepwise refinement design methodology of real-time software: First as we extend general timed automata by distillations and the control of th guishing between internal and external events, this timed automata are suitable for stepwise specifying and designing real-time software. Next we automatically verify whether there exists a timed weak simulation relation from the concrete specification to the abstract one. To the best of our knowledge, a timed weak simulation verification methods of timed automata have never been developed

#### References

before now.

J.W.S. Liu.: Real-Time System, Prentice-Hall (2000).

R. Alur, D.L. Dill.: A theory of timed automatoa, Theoretical Computer Science, Vol. 126, pp.183-235 (1994).

3. Giorgio C. Buttazzo.: Hard Real-Time Computing Systems, Kluwer Academic Publishers (1987).

4. R. Milner.: Operational and Algebraic Semantics of Concurrent Processes. Handbook of Theoretical Computer Science, MIT Press, pp. 1201-1242 (1990)

5. R. Alur, L. Fix, T.A. Henzinger.: Event-Clock Automata: A Determinizable Class of Timed Automata, in Proc. of CAV'94, LNCS 818, pp.1-13 (1994).

6. C. Dima.: Removing slient transitions from event-clock automata, in Proc. of CITTI 2000, pp 75-81 (2000).

7. A. Pnueli.: Linear and Branching Structures in the Semantics and Logics of Reactive Systems. ICALP 1985, volume 194 of LNCS, pp. 15-32 (1985).

8. K. Cerans.: Decidability of bisimulation equivalences for parallel timer processes. LNCS 663, pp. 269-300, Springer Verlag (1992).

9. S.Tasiran, R.Alur, R.P.Kurshan, and R.K.Brayton. : Verifying Abstractions of

Timed Systems. LNCS 1119, pp.546-562, Springer Verlag (1996).

10. V.Braberman, M.Felder.: Verification of Real-Time Designs: Combining Schedul-

ing Theory with Automatic Formal Verification, LNCS 1687, pp.494-510(1999)

11. T. Henzinger, X. Nicollin, J. Sifakis, S. Yovine. : Symbolic model checking for real-time systems, Information and Computation 111, pp.193–244(1994).

12. M. Joseph.: Real-Time System Specification, Verification and Analysis. Prentice Hall (1996).

13. R. Alur, T.A. Henzinger, P.-H. Ho.: Automatic symbolic verification of embedded systems. IEEE Trans. on Software Engineering 22(3), pp.181-201(1996)

14. T.A. Henzinger, P.W. Kopke, A. Puri, and P. Varaiya.: What's decidable about hybrid automata? Journal of Computer and System Sciences 57, pp.94–124(1998).